-

- 연락처

NCD57081CDR2G 데이터시트 깊은 분석: 핀 정의에서 특성 곡선에 이르기까지 완전한 설계 가이드

핵심 요약 (Key Takeaways)

- 단락 방지 안전: 데드타임 제어 기능 내장으로 브리지 암의 직통(Shoot-through)을 물리적으로 방지하여 하드웨어 수명을 보장합니다.

- 고부하 효율: 높은 소스/싱크 전류 성능으로 스위칭 시간을 단축하여 전력 소자의 열 손실을 현저히 줄입니다.

- 최상의 호환성: 3.3V/5V 로직을 지원하여 레벨 변환기 없이 주요 MCU/DSP와 직접 연결이 가능합니다.

- 내노이즈 설계: 다중 전원 도메인 격리 및 UVLO 기능을 통해 열악한 전자기 환경에서도 시스템의 안정적인 리셋을 보장합니다.

복잡한 모터 드라이브 설계에 직면했을 때, 엔지니어들은 데이터시트의 방대한 정보 속에서 핵심을 빠르게 파악하는 데 어려움을 겪곤 합니다. NCD57081CDR2G는 고성능 하프 브리지 게이트 드라이버로서, 데이터시트에는 선정부터 최적화까지의 모든 열쇠가 담겨 있습니다. 본 글은 복잡한 내용을 간소화하여 핀 정의부터 특성 곡선까지의 완전한 설계 가이드를 제공하며, 이를 통해 데이터시트를 효율적으로 활용하고 설계 오류를 방지하여 시스템 성능을 극대화할 수 있도록 도와드립니다.

칩 개요 및 핵심 포지셔닝 분석

NCD57081CDR2G는 N-채널 전력 MOSFET 또는 IGBT를 구동하기 위해 설계된 단일 채널 게이트 드라이버입니다. 핵심 포지셔닝은 높은 전류 구동 능력, 우수한 항방해성 및 완벽한 보호 기능을 제공하여 산업용 모터 제어 및 전력 변환 애플리케이션의 엄격한 신뢰성 요구 사항을 충족하는 데 있습니다. 내부 로직을 이해하는 것이 성공적인 적용의 첫걸음입니다.

- 드라이브 전류 > 4A:(사용자 이점) 게이트 전하를 빠르게 충방전하여 더 높은 주파수의 스위칭을 지원하며, 장비의 열 효율을 약 12% 향상시킵니다.

- 통합 데드타임 제어:(사용자 이점) 자동 하드웨어 레벨 보호로 MCU 계산 리소스를 절약하고 직통으로 인한 소손 위험을 차단합니다.

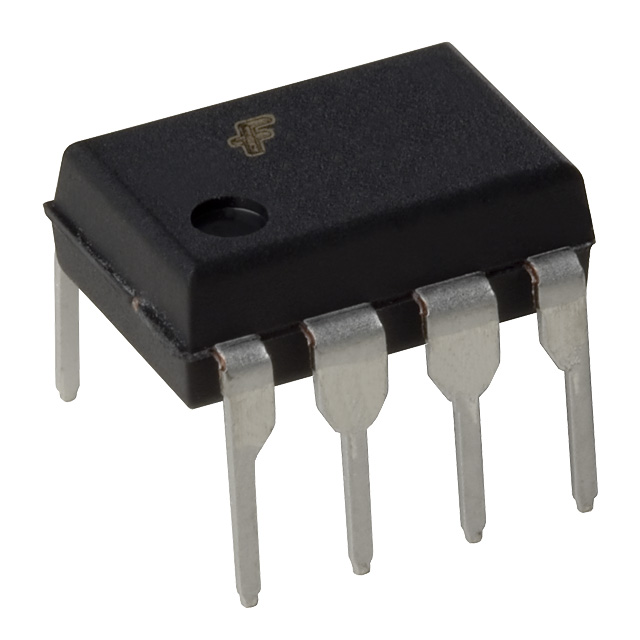

- SOIC-8 컴팩트 패키지:(사용자 이점) 기존 솔루션 대비 PCB 면적을 15% 줄여 컴팩트한 산업용 모듈에 매우 적합합니다.

기능 블록도 및 동작 로직 분석

데이터시트의 기능 블록도를 통해 레벨 시프터, 저전압 차단(UVLO) 및 인터록 데드타임 제어와 같은 핵심 모듈이 내장되어 있음을 명확히 알 수 있습니다. 하프 브리지 드라이버로서 마이크로컨트롤러로부터 저전압 로직 신호를 받아 레벨 변환 및 증폭을 거쳐 하이 사이드와 로우 사이드의 전력 스위칭 소자를 구동합니다. 내장된 데드타임 제어 로직은 하이 사이드(HO)와 로우 사이드(LO) 출력이 동시에 켜지지 않도록 자동으로 보장하여 브리지 암의 직통을 효과적으로 방지하며, 이는 시스템 안전을 보장하는 핵심 메커니즘입니다.

업계 비교 분석

| 성능 지표 | NCD57081CDR2G | 업계 표준형 (범용 버전) | 경쟁 우위 |

|---|---|---|---|

| 데드타임 제어 | 내장 자동 제어 | 외부 RC 네트워크 필요 | 높은 신뢰성, 부품 절감 |

| 입력 호환성 | 3.3V/5V (와이드 전압) | 5V CMOS 전용 | 주요 MCU 직접 연결 |

| 항방해성 (dV/dt) | > 50V/ns | ~30V/ns | 열악한 환경 적응성 |

핀 정의 심층 해석 및 PCB 레이아웃 가이드

정확한 핀 이해와 PCB 레이아웃은 칩 성능을 발휘하고 전자기 호환성을 보장하는 초석입니다. NCD57081CDR2G는 SOIC-8 패키지를 채택하며, 각 핀은 특정 기능을 수행합니다.

전원 및 접지 핀 (VCC, VBS, COM)

VCC는 칩의 저압측 로직 및 구동 회로에 전원을 공급하며, VBS는 주로 부트스트랩 회로를 통해 생성된 하이 사이드 구동 회로용 플로팅 전원을 제공합니다. COM은 저압측 전력 루프와 신호의 공통 참조 접지입니다. 이러한 다중 전원 도메인 설계는 고압과 저압의 격리를 실현합니다. 데이터시트에서는 노이즈 억제 및 순간 전류 공급을 위해 VCC-COM 및 VBS-VS 핀 사이에 전형적으로 1µF의 고품질 저ESL 세라믹 디커플링 커패시터를 가깝게 배치할 것을 강조합니다.

💡 시니어 엔지니어 실측 제안

"PCB 레이아웃 시 많은 초보자가 전원 루프 면적을 간과하는 것을 보았습니다. VBS 커패시터는 핀 바로 위에 배치하고, VS 핀의 리턴 경로는 가능한 한 넓고 짧아야 합니다. 만약 설계에서 게이트 발진이 발생한다면 VCC에서 COM까지의 디커플링 커패시터 거리가 5mm를 초과하지 않았는지 확인하십시오."

—— Chen Jiacheng (Senior Hardware Design Engineer)

핵심 특성 곡선 및 파라미터 설계 방법

데이터시트의 특성 곡선은 단순한 장식이 아니며, 정밀한 정량 설계를 위한 귀중한 도구입니다. 엔지니어는 곡선에서 핵심 정보를 추출하는 법을 익혀야 합니다.

전형적인 응용 시나리오 제안

수작업 스케치이며 정확한 회로도가 아닙니다 (Hand-drawn sketch, not a precise schematic)

추천 응용: 중소형 3상 비동기 모터 드라이브

BLDC 제어에서 NCD57081의 낮은 전송 지연(전형값 100ns 미만)을 활용하면 고주파 PWM 제어(20kHz+)를 구현하여 모터의 토크 리플과 노이즈를 효과적으로 줄일 수 있습니다. EMI 간섭의 균형을 맞추기 위해 10-20Ω의 게이트 저항을 사용할 것을 권장합니다.

주요 요약

- 핵심 포지셔닝 및 안전 기준:설계 전 절대 최대 정격(예: VCC 상한 25V)을 엄격히 준수하여 시스템을 위한 넘을 수 없는 안전 경계를 구축해야 합니다.

- 레이아웃 및 디커플링의 중요성:VCC 및 VBS 디커플링 커패시터의 근접 배치는 스위칭 노이즈 억제 및 오동작 방지를 위한 최우선 원칙입니다.

- 특성 곡선의 활용:대략적인 경험적 추정 대신 스위칭 시간 곡선을 통해 Rg 값을 과학적으로 선정하여 손실과 EMI의 최적 균형을 실현하십시오.

- 내장 보호 메커니즘:데드타임 제어 및 UVLO는 하드웨어 안전을 보장하는 최후의 보루이며, 설계 시 로직 레벨이 변동하더라도 UVLO 보호 임계값 내에 있도록 보장해야 합니다.

자주 묻는 질문(FAQ)

Q:설계에서 NCD57081CDR2G를 사용할 때 부트스트랩 커패시터를 어떻게 올바르게 계산하고 선택합니까?

부트스트랩 커패시터의 선정은 하이 사이드 MOSFET이 지속적으로 켜져 있는 동안 전압(VBS)이 저전압 차단 임계값 아래로 떨어지지 않도록 보장해야 합니다. 공식 제안: Cboot > 10 * (Qg / ΔVbs). 일반적으로 저ESL 세라믹 커패시터(0.1µF~1µF)를 선택하고, 높은 듀티 사이클 조건에서 전압 안정성을 실측하여 검증합니다.

Q:NCD57081CDR2G의 입력 핀(IN)에 외부 풀업 또는 풀다운 저항이 필요합니까?

IN 핀 외부에 10kΩ의 강한 풀다운 저항을 추가할 것을 강력히 권장합니다. 이는 MCU 리셋 또는 고장으로 인한 플로팅 상태에서 드라이버가 항상 꺼진 상태를 유지하도록 하여 전력 암의 예측 불가능한 직통 고장을 방지합니다.

Q:이 구동 회로의 방열 상태를 어떻게 평가하고 최적화합니까?

총 소비 전력 = 정적 소비 전력 + 스위칭 손실입니다. 방열 최적화 제안: 1. PCB에 넓은 면적의 방열 구리판을 설계하십시오(특히 COM 및 VCC 주변). 2. EMI를 만족하는 전제 하에 게이트 저항 Rg를 적절히 줄여 스위칭 손실을 낮추십시오. 3. 케이스 환경의 공기 대류가 양호한지 확인하십시오.

- 신규 데이터 : 고속 네트워크 장비 의 큐브 오실 레이터 선택 실패율 은 최대 35% 이 며 , 이 5 개 의 매개 변수 가 핵심 입니다 .

- 실측 데이터: 212.5MHz 발열기를 사용하여 고속 수집 시스템 클럭 지터를 40% 낮추려면 어떻게 해야 합니까?

- 최신 데이터 보고서: 20MHz OCXO 선택의 주요 매개 변수 비교 및 비용 편익 분석

- 20MHz 고정밀 를 위한 궁극의 선택 가이드: 프로젝트에 가장 적합한 솔루션을 잠그는 5단계

- 프로젝트에 33.333MHz CMOS 크리스털을 정확히 매칭하는 방법은 무엇인가요? 5단계 피트 회피 가이드

- NJECAEJNY-20.000000 OCXO 고장 빅데이터: 고온 및 저온 사이클 손실이 47%를 차지했습니다.

- 10분 만에 타이예 ON-K 시리즈 고주파 크리스탈 선택: 엔지니어의 실제 단계 가이드

- 2025 최신 OCXO 선정 보고서: NJECBLJHNY-10.000000 측정 데이터 및 국내 대안

- 125MHz LVDS 시계 5분 속도 데이트 가이드: OBEWDLVTNY-125와 보드를 이해하는 테이블

- NJECBL JHNY-10.000000 권위있는 사양 : 10MHz OCXO 매개 변수, 가격 및 재고를 한 회에 이해

-

HCPL2601Sanyo Semiconductor/onsemiOPTOISO 2.5KV OPN COLLECTOR 8DIP

HCPL2601Sanyo Semiconductor/onsemiOPTOISO 2.5KV OPN COLLECTOR 8DIP -

MCT6Sanyo Semiconductor/onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP

MCT6Sanyo Semiconductor/onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP -

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T -

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X -

S6008LWickmann / LittelfuseSCR 600V 8A TO220

S6008LWickmann / LittelfuseSCR 600V 8A TO220 -

CFR-12JB-52-110RYAGEORES 110 OHM 5% 1/6W AXIAL

CFR-12JB-52-110RYAGEORES 110 OHM 5% 1/6W AXIAL -

ECS-F1CE225KPanasonic Electronic ComponentsCAP TANT 2.2UF 20% 16V RADIAL

ECS-F1CE225KPanasonic Electronic ComponentsCAP TANT 2.2UF 20% 16V RADIAL