-

- 連絡先

NCD57081CDR2G データシートの詳細解説:ピン定義から特性曲線に至るまでの完全な設計ガイド

主な要点 (Key Takeaways)

- 短絡防止:デッドタイム制御を内蔵し、物理レベルでブリッジアームの貫通を防止、ハードウェアの寿命を保証します。

- 高負荷効率:高いソース/シンク電流能力によりスイッチング時間を短縮し、パワー管の熱損失を大幅に低減します。

- 優れた互換性:3.3V/5Vロジックをサポートし、レベル変換なしで主要なMCU/DSPに直接接続可能です。

- 耐ノイズ設計:マルチ電源ドメイン絶縁とUVLO機能により、過酷な電磁環境下でも安定したシステムリセットを確保します。

複雑なモーター駆動設計に直面した際、エンジニアはデータシートの情報が煩雑で、核心を素早く把握するのが難しいと感じることが多いのではないでしょうか?NCD57081CDR2Gは高性能なハーフブリッジ・ゲートドライバであり、そのデータシートには選定から最適化までの完全な鍵が隠されています。本記事では、ピン定義から特性曲線までを簡潔にまとめ、設計ガイドとして提供します。これにより、データシートを効率的に活用し、設計上の落とし穴を回避してシステム性能を最大限に引き出すことができます。

チップの概要とコア・ポジショニングの解析

NCD57081CDR2Gは、Nチャネル・パワーMOSFETまたはIGBTの駆動用に設計されたシングルチャネル・ゲートドライバです。その核心的な位置付けは、産業用モーター制御や電力変換などの用途における厳しい信頼性要求を満たすため、高い電流駆動能力、優れた耐ノイズ性、および充実した保護機能を提供することにあります。内部ロジックを理解することが、設計成功への第一歩です。

- 駆動電流 > 4A:(ユーザーメリット) ゲート電荷を高速に充放電し、より高い周波数のスイッチングをサポート。デバイスの熱効率を約12%向上させます。

- デッドタイム制御内蔵:(ユーザーメリット) ハードウェアレベルでの自動保護により、MCUの計算リソースを節約し、貫通による焼損リスクを排除します。

- SOIC-8 コンパクトパッケージ:(ユーザーメリット) 従来のソリューションに比べPCB面積を15%削減でき、コンパクトな産業用モジュールに最適です。

機能ブロック図と動作ロジックの分解

データシートの機能ブロック図から、レベルシフト、低電圧ロックアウト(UVLO)、インターロック式デッドタイム制御などの主要モジュールが統合されていることが明確にわかります。ハーフブリッジドライバとして、マイコンからの低圧ロジック信号を受け取り、レベル変換と増幅を経て、ハイサイドおよびローサイドのパワースイッチを駆動します。内蔵されたデッドタイム制御ロジックは極めて重要で、ハイサイド(HO)とローサイド(LO)の出力が同時にオンにならないよう自動的に保証し、システムの安全を確保する核心的なメカニズムであるブリッジアームの貫通を効果的に防止します。

業界比較分析

| 性能指標 | NCD57081CDR2G | 業界標準型 (汎用版) | 競争優位性 |

|---|---|---|---|

| デッドタイム制御 | 自動制御内蔵 | 外部RCネットワークが必要 | 高信頼性、部品削減 |

| 入力互換性 | 3.3V/5V (広電圧) | 5V CMOSのみ | 主要なMCUに直結可能 |

| 耐ノイズ性 (dV/dt) | > 50V/ns | ~30V/ns | 過酷な環境に対応 |

ピン定義の深度解読とPCBレイアウトガイド

正しいピンの理解とPCBレイアウトは、チップの性能を発揮し、電磁両立性(EMC)を確保するための基石です。NCD57081CDR2GはSOIC-8パッケージを採用しており、各ピンには特定の機能があります。

電源および接地ピン(VCC, VBS, COM)

VCCはチップのローサイドロジックおよび駆動回路に電力を供給します。VBSはハイサイド駆動回路に浮動電源を供給し、通常はブートストラップ回路によって生成されます。COMはローサイド電力ループと信号の共通リファレンス接地です。このマルチ電源ドメイン設計により、高低圧の絶縁を実現しています。データシートでは、ノイズを抑制し瞬時電流を供給するために、VCCとCOM、VBSとVSピンの間に、高品質で低ESLのセラミックデカップリングコンデンサ(標準値1µF)をできるだけ近くに配置することを強調しています。

💡 ベテランエンジニアの実測アドバイス

「PCBレイアウトを行う際、多くの初心者が電源ループ面積を見落としていることに気づきます。VBSコンデンサはピンの直上に配置し、VSピンの還流経路は可能な限り広く短くすることをお勧めします。設計中にゲート振動が発生した場合は、VCCからCOMへのデカップリングコンデンサが5mm以上の物理的距離になっていないか確認してください。」

—— 陳嘉誠 (シニア・ハードウェア設計エンジニア)

コア特性曲線とパラメータ設計手法

データシートの特性曲線は単なる飾りではなく、精密な定量的設計を行うための貴重なツールです。エンジニアは曲線から重要な情報を抽出する方法を学ぶべきです。

典型的な応用シーンの提案

手書きイメージ、正確な回路図ではありません (Hand-drawn sketch, not a precise schematic)

推奨用途:中小型三相誘導モーター駆動

BLDC制御において、NCD57081の低伝搬遅延(標準100ns以下)を利用することで、高周波PWM制御(20kHz以上)が可能となり、モーターのトルクリップルやノイズを効果的に低減できます。EMI対策として、10〜20Ωのゲート抵抗を併用することをお勧めします。

重要なまとめ

- コア・ポジショニングと安全基準:設計前に絶対最大定格(25V VCC上限など)を厳守し、システムに越えてはならない安全境界を確立する必要があります。

- レイアウトとデカップリングが鍵:VCCおよびVBSデカップリングコンデンサの至近配置は、スイッチングノイズを抑制し、誤トリガを防止するための第一原則です。

- 特性曲線の活用:スイッチング時間曲線を通じてRg値を科学的に選定し、大まかな経験則を排して、損失とEMIの最適なバランスを実現します。

- 内蔵保護メカニズム:デッドタイム制御とUVLOはハードウェア安全の生命線です。ロジックレベルが変動してもUVLO保護閾値内に留まるように設計してください。

よくある質問 (FAQ)

Q:設計でNCD57081CDR2Gを使用する際、ブートストラップコンデンサをどのように正しく計算し選定すればよいですか?

ハイサイドMOSFETがオンし続けている間、電圧(VBS)が低電圧ロックアウト閾値を下回らないように選定する必要があります。推奨式:Cboot > 10 * (Qg / ΔVbs)。一般的には低ESRセラミックコンデンサ(0.1µF〜1µF)を選択し、高デューティサイクルの条件下で電圧の安定性を実測検証してください。

Q:NCD57081CDR2Gの入力ピン(IN)に外部のプルアップまたはプルダウン抵抗は必要ですか?

INピンの外部に10kΩの強力なプルダウン抵抗を追加することを強く推奨します。これにより、MCUのリセット時や故障によるフローティング状態でドライバを常にオフ状態に保ち、パワーアームの予期せぬ貫通故障を防止できます。

Q:この駆動回路の放熱状況をどのように評価し最適化すればよいですか?

総消費電力 = 静的消費電力 + スイッチング損失。放熱最適化の提案:1. PCB上に広面積の放熱用銅箔を設計する(特にCOMとVCC周辺)。2. EMIを考慮しつつ、ゲート抵抗Rgを適度に小さくしてスイッチング損失を低減する。3. ケース周囲の空気対流が良好であることを確認する。

- 最新データ:高速ネットワーク機器の水晶発振器の選定失敗率は35%と高く、この5つのパラメータが重要である

- 測定データ: 212.5 MHz発振器を使用して、高速収集システムのクロックジッタを40%削減する方法は?

- 2025低ジッタクロックセレクションの究極のガイド:高周波XOを正確にマッチングするための5つのステップ、パフォーマンスの無駄に別れを告げる

- OMENGLVAKY-212.500000 データシート 完全分解:寸法と電気的特性を一目でご覧ください

- 最新データ報告書:20MHz OCXO選択の主要パラメータの比較および費用対効果分析

- 20MHz高精度発振器の究極選択ガイド:プロジェクトに最適なソリューションを確実にするための5ステップ

- あなたのプロジェクトに33.333 MHz CMOS水晶発振器を正確にマッチングする方法は?5つのステップで落とし穴を避けるガイド

- 原理から実践まで:高速通信システム用の312.5 MHz LV DS発振器を正確に選択し、マッチングする方法は?

- NJECAEJHNY-20.000000 OCXO故障ビッグデータ:高温・低温サイクルによる被害の47%

- 10分でタイ芸ONKシリーズ高周波水晶発振器の選定:エンジニアの実戦ステップガイド

-

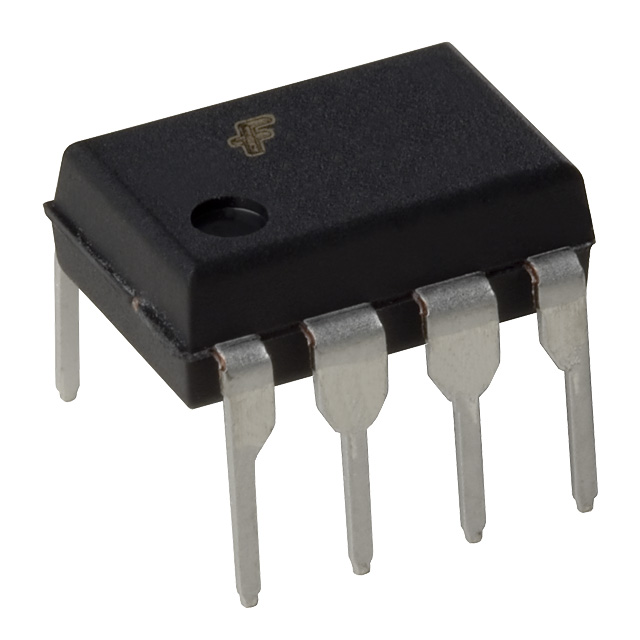

HCPL2601Sanyo Semiconductor/onsemiOPTOISO 2.5KV OPN COLLECTOR 8DIP

HCPL2601Sanyo Semiconductor/onsemiOPTOISO 2.5KV OPN COLLECTOR 8DIP -

MCT6Sanyo Semiconductor/onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP

MCT6Sanyo Semiconductor/onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP -

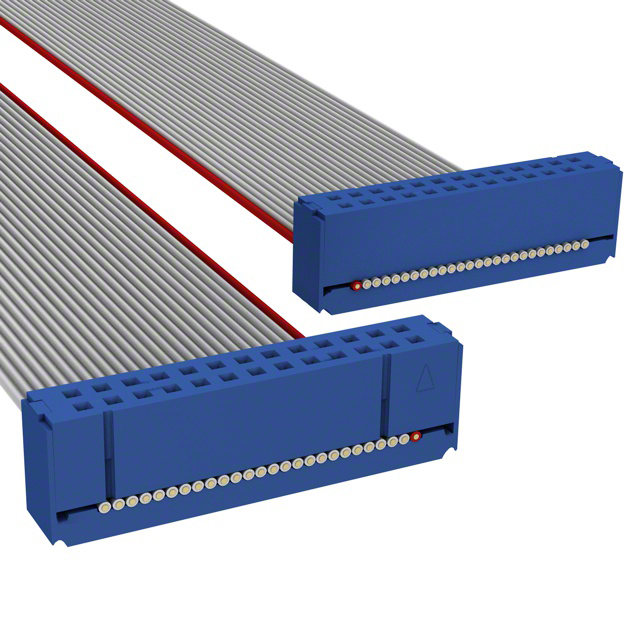

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T -

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X -

S6008LWickmann / LittelfuseSCR 600V 8A TO220

S6008LWickmann / LittelfuseSCR 600V 8A TO220 -

CFR-12JB-52-110RYAGEORES 110 OHM 5% 1/6W AXIAL

CFR-12JB-52-110RYAGEORES 110 OHM 5% 1/6W AXIAL -

ECS-F1CE225KPanasonic Electronic ComponentsCAP TANT 2.2UF 20% 16V RADIAL

ECS-F1CE225KPanasonic Electronic ComponentsCAP TANT 2.2UF 20% 16V RADIAL