-

- 連絡先

私たちを購読しましょう!

人気のある投稿

- 最新データ:高速ネットワーク機器の水晶発振器の選定失敗率は35%と高く、この5つのパラメータが重要である

- 測定データ: 212.5 MHz発振器を使用して、高速収集システムのクロックジッタを40%削減する方法は?

- 2025低ジッタクロックセレクションの究極のガイド:高周波XOを正確にマッチングするための5つのステップ、パフォーマンスの無駄に別れを告げる

- OMENGLVAKY-212.500000 データシート 完全分解:寸法と電気的特性を一目でご覧ください

- 最新データ報告書:20MHz OCXO選択の主要パラメータの比較および費用対効果分析

- 20MHz高精度発振器の究極選択ガイド:プロジェクトに最適なソリューションを確実にするための5ステップ

- あなたのプロジェクトに33.333 MHz CMOS水晶発振器を正確にマッチングする方法は?5つのステップで落とし穴を避けるガイド

- 原理から実践まで:高速通信システム用の312.5 MHz LV DS発振器を正確に選択し、マッチングする方法は?

- NJECAEJHNY-20.000000 OCXO故障ビッグデータ:高温・低温サイクルによる被害の47%

- 10分でタイ芸ONKシリーズ高周波水晶発振器の選定:エンジニアの実戦ステップガイド

人気のある部品

-

IN 500-SLEM USA, Inc.500A ULTRA ACCURACY

IN 500-SLEM USA, Inc.500A ULTRA ACCURACY -

IN 200-SLEM USA, Inc.200A ULTRA ACCURACY

IN 200-SLEM USA, Inc.200A ULTRA ACCURACY -

IN 400-SLEM USA, Inc.400A ULTRA ACCURACY

IN 400-SLEM USA, Inc.400A ULTRA ACCURACY -

IN 1200-SLEM USA, Inc.1200A ULTRA ACCURACY

IN 1200-SLEM USA, Inc.1200A ULTRA ACCURACY -

IN 2000-SLEM USA, Inc.2000A ULTRA ACCURACY

IN 2000-SLEM USA, Inc.2000A ULTRA ACCURACY -

IN 2000-SBLEM USA, Inc.2000A ULTRA ACCURACY

IN 2000-SBLEM USA, Inc.2000A ULTRA ACCURACY -

PI3EQX32908EZRIEXZetex Semiconductors (Diodes Inc.)USB3 EQX W-QFN3590-62 T&R 3.5K

PI3EQX32908EZRIEXZetex Semiconductors (Diodes Inc.)USB3 EQX W-QFN3590-62 T&R 3.5K -

FF3MR12KM1HPHPSA1IR (Infineon Technologies)FF3MR12KM1HPHPSA1

FF3MR12KM1HPHPSA1IR (Infineon Technologies)FF3MR12KM1HPHPSA1 -

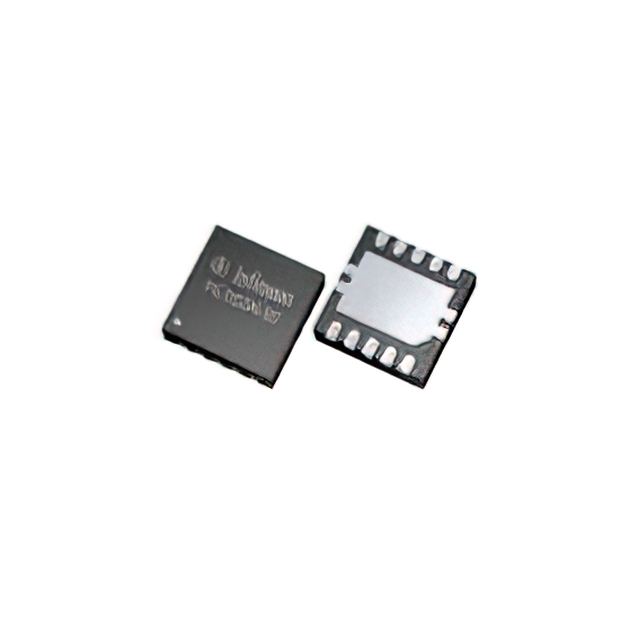

2ED2778S01GXTMA1IR (Infineon Technologies)2ED2778S01GXTMA1

2ED2778S01GXTMA1IR (Infineon Technologies)2ED2778S01GXTMA1 -

2ED2772S01GXTMA1IR (Infineon Technologies)2ED2772S01GXTMA1

2ED2772S01GXTMA1IR (Infineon Technologies)2ED2772S01GXTMA1