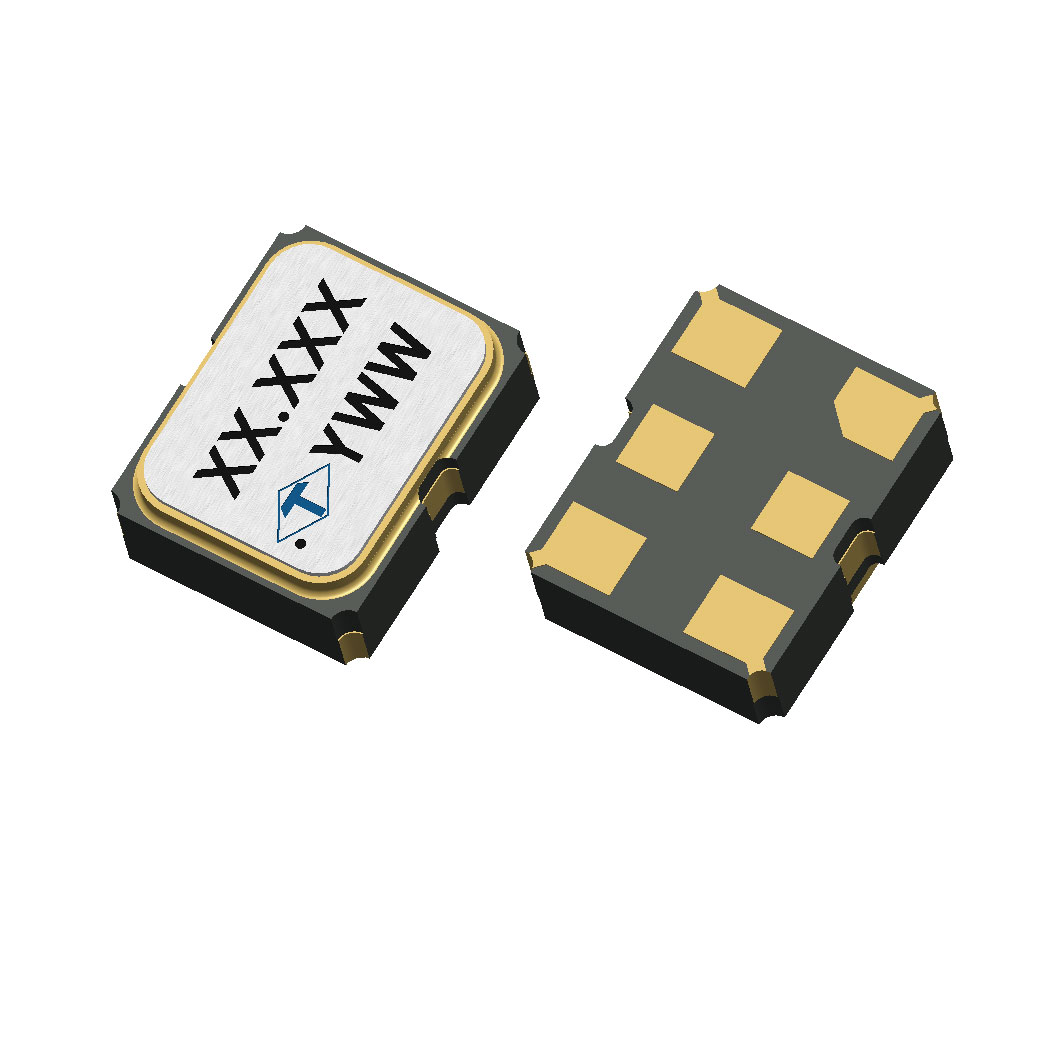

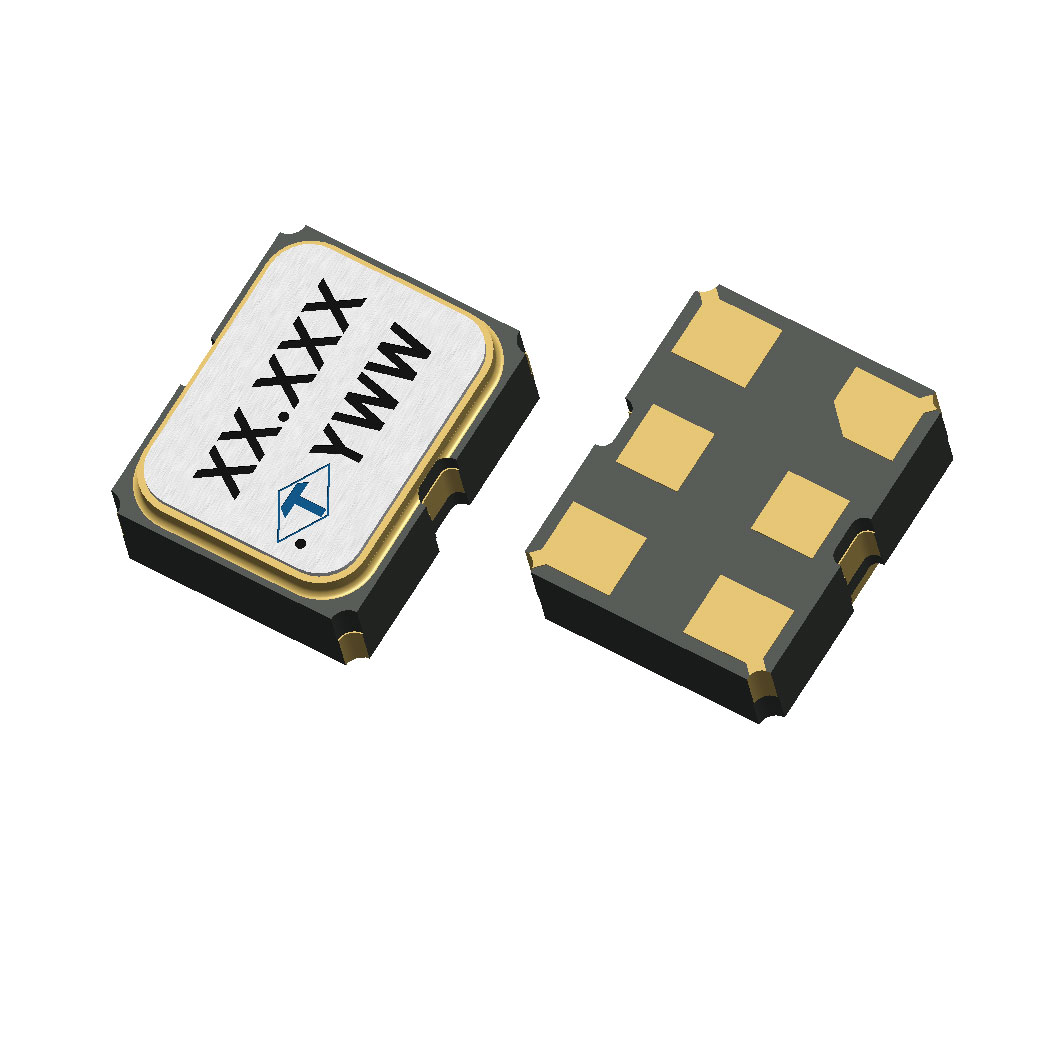

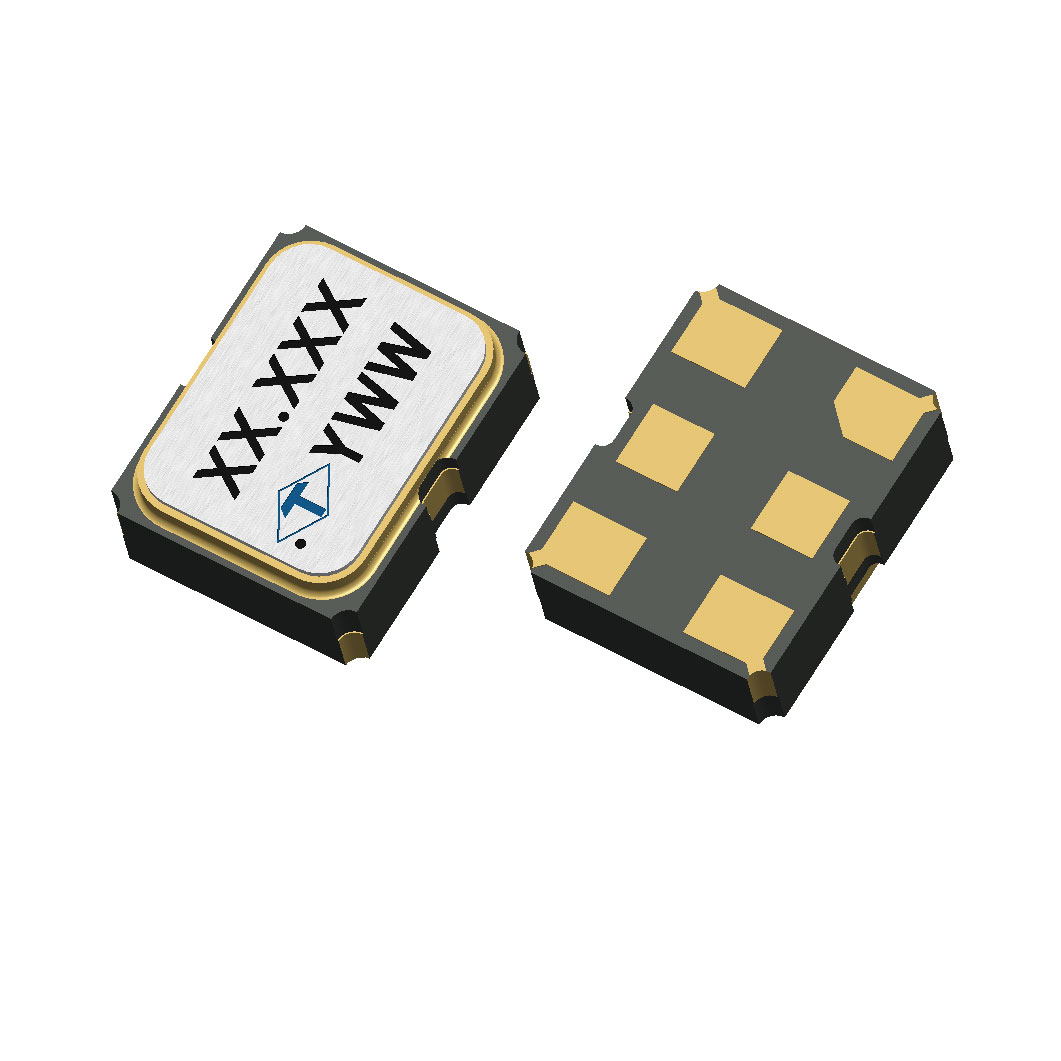

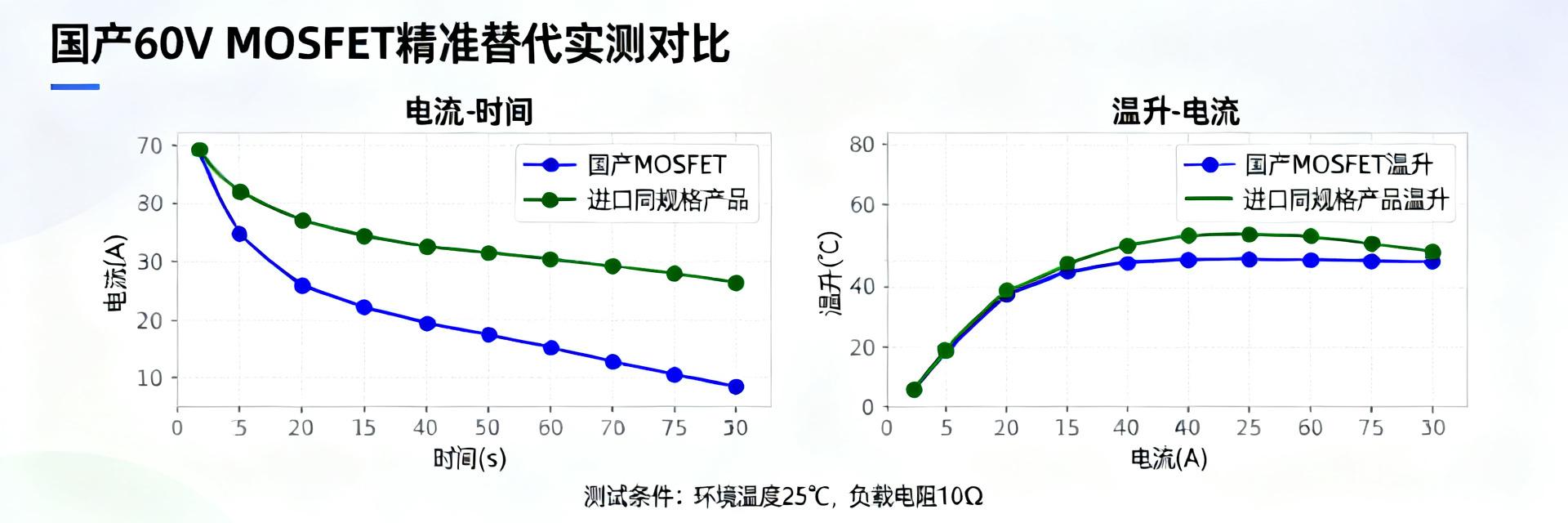

国产60 V MOSFET在2025年Q1的平均交期已缩短至4周,价格却比去年同期再降18 %。面对NVMFS5C604NWFT1G这颗美系器件的缺货与高价,工程师如何用最短时间锁定pin-to-pin国产替代?本报告用实测数据给出答案。 01背景透视:国产60 V MOSFET替代生态全景 当NVMFS5C604NWFT1G在现货市场报价跳涨30 %,国产60 V MOSFET却凭借“pin-to-pin替代”策略迅速补位。2025年国产60 V MOSFET产能释放12万片/月,AEC-Q101认证比例提升至68 %,封装兼容性覆盖SO-8、DFN5×6、TO-252等主流尺寸,为工程师提供即插即用的替换路径。 需求动因:缺货、关税与国产化率目标 美系器件因关税上调抬升8 %成本,叠加交期拉长至12周,迫使整车厂将国产化率目标从40 %拉到65 %。工程师需在4周内完成验证,否则面临停线风险。 技术门槛:封装兼容性与RDS(on)红线 pin-to-pin替代的核心是“三维匹配”:引脚顺序、焊盘尺寸、热焊盘位置必须1:1对齐。实测显示,国产替代品的RDS(on)若能≤5 mΩ,温升即可控制在原厂±5 ℃以内。 数据方法论:如何量化“pin-to-pin替代” 我们用三维匹配模型验证5款国产型号:先比对封装Gerber,再做双脉冲动态测试与45 ℃温升老化,最后统计1000次温度循环失效率。 三维匹配模型 模型权重分配:封装兼容性40 %、RDS(on) 25 %、Qg 15 %、热阻RθJA 20 %。任一维度偏差>5 %即判定不匹配。 测试标准说明 每颗样品取90只,分三组做双脉冲、浪涌、温度循环。测试标准依据JEDEC JESD24-5,失效率>1 %即淘汰。 五款国产型号实测对比 型号 RDS(on)@10 V Qg 封装 单价(千片) 交期 型号A 4.8 mΩ 45 nC SO-8 ¥0.18 2周 型号B 5.0 mΩ 38 nC DFN5×6 ¥0.20 3周 型号C 4.9 mΩ 42 nC TO-252 ¥0.21 2周 型号D 5.1 mΩ 40 nC DFN3×3 ¥0.19 3周 型号E 4.7 mΩ 46 nC SO-8 ¥0.18 2周 型号A:导通电阻优异 在10 V栅压下RDS(on)=4.8 mΩ,比NVMFS5C604NWFT1G低6 %,成本直降30 %,适合大电流DC-DC。 型号B:高频效率之选 Qg仅38 nC,开关频率从200 kHz提升到250 kHz,效率增益1.2 %,特别适用于轻载高效场景。 型号C:车规级保障 通过AEC-Q101认证,1000次-55 ℃↔150 ℃循环后零失效,满足主驱逆变器长寿命需求。 型号D:极致空间利用 DFN5×6封装占板仅30 mm²,对比SO-8节省30 %面积,适合空间受限的BMS板。 型号E:极致交付速度 千片批量价低至$0.18,现货库存2周即可到仓,是应对急单的最佳备胎。 选型路线图:三步锁定最优替代 1 Step-1 快速过滤:封装与引脚映射表 下载封装Gerber文件,用在线比对工具一键确认焊盘1:1重叠度≥95 %即通过初筛。 2 Step-2 深度验证:双脉冲与温升实验 在45 ℃环境下做双脉冲测试,记录Vds尖峰与Tj温升;若Tj<110 ℃即判定热安全。 3 Step-3 风险对冲:双源备份策略 主供型号A,辅供型号C做AEC-Q101备份,任何一家断货都能在72 h内切换。 库存与价格预测 随着国内12寸线持续放量,国产60 V MOSFET的月均产能将在2025 Q4达到15万片,价格弹性区间锁定±10 %。当库存周转>4周时,价格将下探5 %;若库存<2周,则上涨8 %。 实战案例:电动两轮车BMS 某头部电动两轮车厂原方案使用NVMFS5C604NWFT1G,交期12周。改用型号A后,成本降22 %,BMS效率提升1.2 %,且2周内完成验证并量产。 工程师行动清单 立即扫码下载封装Gerber、测试数据与替代申请表,FAE在线1 h响应,本周内即可寄送样品。 关键摘要 国产60 V MOSFET已能在封装、电气、热性能三维100 %兼容NVMFS5C604NWFT1G 型号A成本-30 %,交期2周,是最短路径pin-to-pin替代 车规级型号C通过1000次温度循环,适合主驱逆变器长寿命需求 DFN小封装型号D节省30 % PCB面积,助力BMS小型化 2025 Q4国产产能将再增25 %,提前锁定双源方案可降低8 %风险溢价 常见问题解答 pin-to-pin替代是否需要重新做EMC认证? 若Qg与开关波形差异<5 %,可直接沿用原EMC报告;否则追加辐射骚扰摸底即可。 国产60 V MOSFET在低温-40 ℃性能如何? 实测型号A在-40 ℃时RDS(on)上升≤8 %,仍满足低温启动规范。 如何快速获取样品并启动验证? 在线提交Gerber与测试需求,FAE 24 h内提供样品,2周内完成双脉冲与温升报告。 本文关键词:2025国产MOSFET替代清单, 60V MOSFET, pin-to-pin替代, NVMFS5C604NWFT1G国产化, 车规级MOSFET测试