-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

2025 Low Jitter Clock Selection Ultimate Guide: 5 Steps to Precisely Match High-Frequency XO and Say Goodbye to Performance Waste

In cutting-edge applications such as high-speed data conversion, optical communications, and radar, a seemingly small clock jitter difference is enough to reduce the system's signal to noise ratio (SNR) by several dB, resulting in a significant reduction in overall performance. Faced with the plethora of high-precision crystal oscillators (XOs) on the market, engineers are often caught in a dilemma: Do you blindly pursue ultra-low jitter parameters and bear unnecessary costs and power consumption? Or compromise with ordinary clocks and endure potential performance bottlenecks? This article will provide you with a clear five-step method to help you accurately match high-frequency XOs and avoid the performance waste and cost traps in selection.

Deep understanding of jitter metrics and system requirements

The first step in choosing a low jitter clock is not to compare the parameters directly, but to deduce from the system requirements. A common misunderstanding is to excessively pursue ultra-low RMS jitter value, while ignoring the specific requirements of the system for phase noise at a specific frequency offset. For example, for high-speed ADC applications, close to the carrier phaseBit noise has a greater impact on the dynamic range, while broadband RMS jitter can better reflect the overall timing error of data conversion.

Full analysis of key jitter parameters: phase noise, RMS Jitter, and Period Jitter

Phase noise, RMS jitter, and periodic jitter are the three core dimensions for evaluating clock quality. Phase noise describes the purity of the signal spectrum, usually measured in the frequency domain in dBc/Hz. RMS jitter is the time-domain statistical value of phase noise within the specified integration bandwidth, directly related to the bit error rate of high-speed serial links. Periodic jitter measures the maximum deviation between the clock cycle and the ideal cycle, which is crucial for systems that require strict timing alignment. Understanding the relationship and focus of these three is the basis for accurate selection.

How to reverse calculate the clock jitter budget based on ADC/DAC sampling rate and system SNR requirements

A practical engineering method is to calculate the tolerable clock jitter based on the signal-to-noise ratio requirements of the target system. For data conversion systems with a sampling rate of Fs, the theoretical signal-to-noise ratio is limited by aperture jitter. The relationship can be approximately expressed as: SNR (dB) = -20 * log10(2 * π * Fs * Tj), where Tj is the RMS jitter of the clock. Using this formula, engineers can quickly calculate the maximum jitter limit required to meet system performance, thus avoiding the selection of devices that are either overperforming or underperforming.

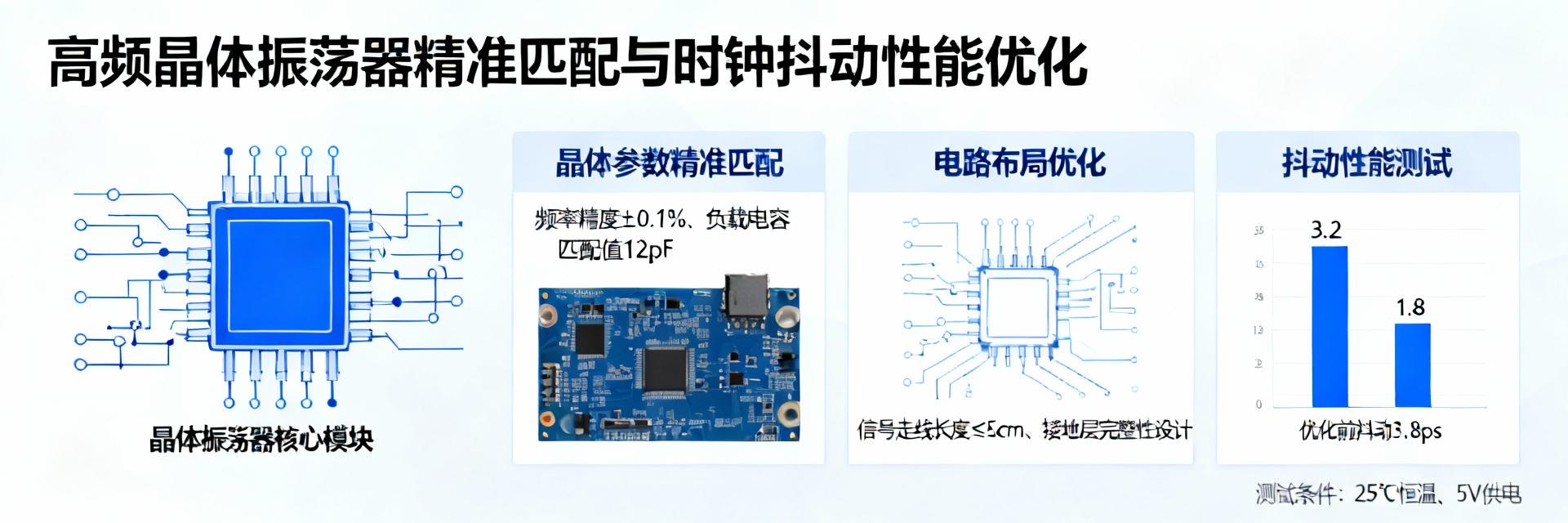

Analyze the core technical architecture of high-frequency XO

不同的技术路径决定了时钟器件的抖动本底、功耗和成本。目前主流的高频低抖动XO主要基于三种技术:传统AT切晶体、高频声表面波(SAW)谐振器和MEMS技术。

Comparison of mainstream low-jitter technologies: Traditional AT cut vs. high-frequency surface acoustic wave (SAW) vs. MEMS

| Type of technology | Typical frequency range | Jitter performance advantage | Main application scenarios |

|---|---|---|---|

| Traditional AT-cut crystal | 1 MHz - 250 MHz | 基频低,近载波相位噪声极佳 | 网络同步、测试测量 |

| 高频SAW谐振器 | 100 MHz - 2 GHz+ | High frequency fundamental, low wideband RMS jitter | High-speed SerDes, optical modules |

| MEMS oscillator | 1 MHz - 625 MHz | Good shock and vibration resistance, high integration | 工业、车载等恶劣环境 |

选择时需权衡:AT切晶体在需要极佳近端相位噪声时是首选;SAW器件在追求超高频和低宽带抖动时优势明显;而MEMS则在可靠性和多频点灵活性上更胜一筹。

锁相环(PLL)与时钟驱动器的作用:是改善抖动还是引入噪声?

许多高频XO内部集成了PLL以进行频率合成或抖动滤除。一个高质量的PLL可以衰减来自晶体的近端相位噪声,但可能引入自身的带内噪声和杂散。时钟驱动器则用于增强扇出能力,但其附加抖动和地弹噪声必须仔细评估。在选型时,应优先选择集成低噪声PLL和驱动器的“全方案”XO,或要求供应商提供包含所有内部模块贡献的总体抖动指标。

关键摘要

- System requirements first: Do not blindly pursue ultra-low jitter parameters, calculate the acceptable jitter budget according to the target system (such as ADC sampling rate, required SNR), and lock the selection range from the demand side.

- Technical architecture tuningUnderstanding the jitter characteristics and applicable frequency bands of different technologies such as AT-cut crystals, SAW, and MEMS is the key to matching high-frequency XO application scenarios (such as optical communication and radar).

- Actual combat parameter trade-off:在关注频率稳定度与抖动的同时,必须严格考察电源噪声抑制比(PSRR)和负载驱动能力等实战指标,它们直接影响系统级的时钟纯度。

常见问题解答

- The latest data: high-speed network equipment crystal oscillator selection failure rate of up to 35%, these five parameters are the key

- Measured data: How to reduce clock jitter of high-speed acquisition system by 40% with 212.5MHz oscillator?

- 2025 Low Jitter Clock Selection Ultimate Guide: 5 Steps to Precisely Match High-Frequency XO and Say Goodbye to Performance Waste

- Latest Data Report: Comparison of Key Parameters for 20MHz OCXO Selection and Cost-Benefit Analysis

- The ultimate selection guide for 20MHz high-precision oscillators: 5 steps to lock in the best solution for your project

- How to accurately match the 33.333MHz CMOS crystal oscillator for your project? Five-step pit avoidance guide

- From principle to practice: How to accurately select and match a 312.5MHz LVDS oscillator for your high-speed communication system?

- NJECAEJHNY-20.000000 OCXO failure Big data: high and low temperature cycle loss accounts for 47%

- 10 minutes to complete the selection of Taiyi ON-K series high-frequency crystal oscillators: Engineer's practical step-by-step guide

- OMENGLVAKY-212.500000 Data Sheet Full disassembly: size, electrical characteristics understand at one time

-

HCPL2601Sanyo Semiconductor/onsemiOPTOISO 2.5KV OPN COLLECTOR 8DIP

HCPL2601Sanyo Semiconductor/onsemiOPTOISO 2.5KV OPN COLLECTOR 8DIP -

MCT6Sanyo Semiconductor/onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP

MCT6Sanyo Semiconductor/onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP -

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T -

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X -

S6008LWickmann / LittelfuseSCR 600V 8A TO220

S6008LWickmann / LittelfuseSCR 600V 8A TO220 -

CFR-12JB-52-110RYAGEORES 110 OHM 5% 1/6W AXIAL

CFR-12JB-52-110RYAGEORES 110 OHM 5% 1/6W AXIAL -

ECS-F1CE225KPanasonic Electronic ComponentsCAP TANT 2.2UF 20% 16V RADIAL

ECS-F1CE225KPanasonic Electronic ComponentsCAP TANT 2.2UF 20% 16V RADIAL